Fan-Out Wafer Level Packaging Market Report 2026

Global Outlook – By Process Type ( Standard-Density Packaging, High-Density Packaging, Bumping), By Business Model ( Outsourced Semiconductor Assembly and Test (OSAT), Foundry, Integrated Device Manufacturer (IDM)), By Application ( Consumer Electronics, Industrial, Automotive, Healthcare, Aerospace And Defense, IT And Telecommunication, Other Applications) – Market Size, Trends, Strategies, and Forecast to 2035

Fan-Out Wafer Level Packaging Market Overview

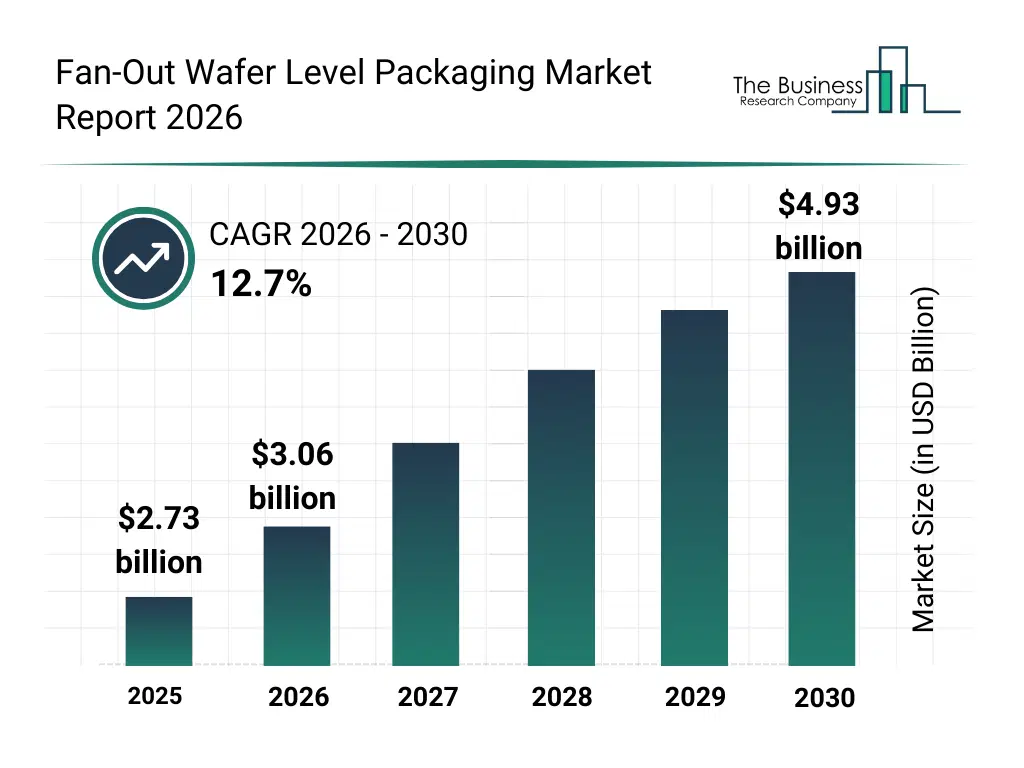

• Fan-Out Wafer Level Packaging market size has reached to $2.73 billion in 2025 • Expected to grow to $4.93 billion in 2030 at a compound annual growth rate (CAGR) of 12.7% • Growth Driver: The Impact Of 5G Adoption On Fan-Out Wafer-Level Packaging In Emerging Market • Market Trend: Technological Advancements In Fan-Out Wafer Level Packaging • Asia-Pacific was the largest region in 2025.What Is Covered Under Fan-Out Wafer Level Packaging Market?

Fan-Out WLP (FOWLP) refers to a technological improvement to regular wafer-level packages (WLPs) designed to provide a solution for semiconductor devices requiring a higher integration level and more significant external contacts. It has a lower package footprint, more input/output (I/O) and better thermal and electrical performance. It has various advantages and can increase the number of connections without increasing the die size. The main types of process of fan-out wafer level packaging are standard-density packaging, high-density packaging and bumping. Standard-density packaging refers to packing density that is close to the theoretical maximum packing density for a given set of objects. The various business models are outsourced semiconductor assembly and test (OSAT), foundry and integrated device manufacturer (IDM) applied in consumer electronics, industrial, automotive, healthcare, aerospace and defense, IT and telecommunication and others.

What Is The Fan-Out Wafer Level Packaging Market Size 2026 And Growth Rate?

The fan-out wafer level packaging market size has grown rapidly in recent years. It will grow from $2.73 billion in 2025 to $3.06 billion in 2026 at a compound annual growth rate (CAGR) of 11.9%. The growth in the historic period can be attributed to growth of mobile and consumer electronics, rising need for compact semiconductor packaging, early development of bumping and rdl technologies, increasing adoption of wafer level packaging, expansion of osat capabilities globally.What Is The Fan-Out Wafer Level Packaging Market Growth Forecast?

The fan-out wafer level packaging market size is expected to see rapid growth in the next few years. It will grow to $4.93 billion in 2030 at a compound annual growth rate (CAGR) of 12.7%. The growth in the forecast period can be attributed to rising demand for heterogeneous integration, expansion of AI and 5g semiconductor requirements, growing automotive electronics adoption, increasing need for enhanced thermal dissipation solutions, growth in advanced packaging investments by foundries and idms. Major trends in the forecast period include growing adoption of high density advanced packaging, increasing use of multi layer redistribution layer technologies, rising demand for miniaturized semiconductor packages, expansion of fan out solutions in automotive and industrial electronics, growing shift toward advanced thermal and electrical performance packaging.Global Fan-Out Wafer Level Packaging Market Segmentation

1) By Process Type: Standard-Density Packaging, High-Density Packaging, Bumping 2) By Business Model: Outsourced Semiconductor Assembly and Test (OSAT), Foundry, Integrated Device Manufacturer (IDM) 3) By Application: Consumer Electronics, Industrial, Automotive, Healthcare, Aerospace And Defense, IT And Telecommunication, Other Applications Subsegments: 1) By Standard-Density Packaging: Die Attach, Redistribution Layer (RDL) Formation, Encapsulation 2) By High-Density Packaging: Fine Pitch RDL, Multi-layer RDL, Advanced Encapsulation Techniques 3) By Bumping: Solder Bump Formation, Copper Pillar Bumping, Microbump TechnologyWhat Is The Driver Of The Fan-Out Wafer Level Packaging Market?

The 5G technology adoption in emerging countries is expected to propel the growth of the fan-out wafer-level packaging market in the coming future. 5G is the fifth generation of cellular network technology designed to increase speed, reduce latency, and improve the flexibility of wireless services. Fan-out wafer-level packaging helps 5G technology by providing shorter interconnects and reduced inductance, enhancing RF and millimeter-wave performance. For instance, in April 2023, according to 5G Americas, a US-based industry trade organization composed of leading telecommunications service providers and manufacturers, 5G is expected to reach 1.9 billion by the end of 2023 and 5.9 billion by the end of 2027, with 32% penetration of the population in North America, and North American 5G connections are projected to hit 215 million by the end of 2023. Therefore, 5G technology adoption in emerging countries is driving the fan-out wafer-level packaging market.Key Players In The Global Fan-Out Wafer Level Packaging Market

Major companies operating in the fan-out wafer level packaging market are Samsung Electronics Co. Ltd., Taiwan Semiconductor Manufacturing Company Limited, Intel Corporation, Qualcomm Inc., Fujitsu Limited, Toshiba Corporation, Applied Materials Inc., ASE Technology Holding Co. Ltd., Texas Instruments Incorporated, Lam Research Corporation, STMicroelectronics N.V., Infineon Technologies AG, NXP Semiconductors N.V., Analog Devices Inc., Renesas Electronics Corporation, United Microelectronics Corporation, GlobalFoundries Inc., Amkor Technology Inc., Microchip Technology Inc., Synopsys Inc, Xilinx Inc., Siliconware Precision Industries Co Ltd, Onto Innovation Inc., Unisem Group, Nepes Corporation, Deca Technologies Inc, Yield Engineering Systems Inc, Powertech Technology Inc., Jiangsu Changdian Technology Co. Ltd., Yole GroupGlobal Fan-Out Wafer Level Packaging Market Trends and Insights

Major companies operating in the fan-out wafer-level packaging market are focusing on technological advancements, such as graphics and generative artificial intelligence (AI) technology, to enhance packaging integration and performance. Graphics and generative artificial intelligence technology refer to advanced computing methods that combine high-performance visual processing with AI models capable of creating, analyzing, and optimizing complex data patterns to enhance system efficiency and functionality. For instance, in October 2023, Samsung Electronics, a South Korea-based semiconductor and electronics company, introduced the Exynos 2400 processor, which features next-generation graphics capability and generative AI inferencing alongside advanced packaging to support enhanced compute demands. The processor offers accelerated AI performance, high-fidelity graphics rendering, and improved power efficiency. This development underscores the positive opportunity for the market in enabling high-performance applications, enabling thinner packages, and greater interconnect density. However, it also reveals challenges, including increased process complexity, higher cost of advanced packaging materials, and thermal management concerns in ultra-dense packages.What Are Latest Mergers And Acquisitions In The Fan-Out Wafer Level Packaging Market?

In October 2024, Amkor Technology, Inc., a U.S.-based company involved in outsourced semiconductor packaging and test services, partnered with ASE Technology Holding Co., Ltd. This strategic partnership aims to leverage Amkor's expertise in flip chip and wafer-level packages and enhance their capabilities in fan-out wafer-level packaging (FOWLP) technology. ASE Technology Holding Co., Ltd. is a China-based company provider of semiconductor packaging and testing services, alongside electronic manufacturing services (EMS).Regional Outlook

Asia-Pacific was the largest region in the fan-out wafer level packaging market in 2025. The regions covered in this market report are Asia-Pacific, South East Asia, Western Europe, Eastern Europe, North America, South America, Middle East, Africa. The countries covered in this market report are Australia, Brazil, China, France, Germany, India, Indonesia, Japan, Taiwan, Russia, South Korea, UK, USA, Canada, Italy, Spain.What Defines the Fan-Out Wafer Level Packaging Market?

The fan-out wafer level packaging market consists of revenues earned by entities by offering services such as substrate-less packages, SiP and 3D integration and built-in back-side protection. The market value includes the value of related goods sold by the service provider or included within the service offering. The fan-out wafer level packaging market also consists of sales of redistribution layers (RDLS), molding compounds, solder balls and carrier wafers. Values in this market are ‘factory gate’ values, that is the value of goods sold by the manufacturers or creators of the goods, whether to other entities (including downstream manufacturers, wholesalers, distributors and retailers) or directly to end customers. The value of goods in this market includes related services sold by the creators of the goods.How is Market Value Defined and Measured?

The market value is defined as the revenues that enterprises gain from the sale of goods and/or services within the specified market and geography through sales, grants, or donations in terms of the currency (in USD unless otherwise specified). The revenues for a specified geography are consumption values that are revenues generated by organizations in the specified geography within the market, irrespective of where they are produced. It does not include revenues from resales along the supply chain, either further along the supply chain or as part of other products.What Key Data and Analysis Are Included in the Fan-Out Wafer Level Packaging Market Report 2026?

The fan-out wafer level packaging market research report is one of a series of new reports from The Business Research Company that provides market statistics, including industry global market size, regional shares, competitors with the market share, detailed market segments, market trends and opportunities, and any further data you may need to thrive in the fan-out wafer level packaging industry. The market research report delivers a complete perspective of everything you need, with an in-depth analysis of the current and future state of the industry.Fan-Out Wafer Level Packaging Market Report 2026 Market Report Forecast Analysis

| Report Attribute | Details |

|---|---|

| Market Size Value In 2026 | $3.06 billion |

| Revenue Forecast In 2035 | $4.93 billion |

| Growth Rate | CAGR of 11.9% from 2026 to 2035 |

| Base Year For Estimation | 2025 |

| Actual Estimates/Historical Data | 2020-2025 |

| Forecast Period | 2026 - 2030 - 2035 |

| Market Representation | Revenue in USD Billion and CAGR from 2026 to 2035 |

| Segments Covered | Process Type, Business Model, Application |

| Regional Scope | Asia-Pacific, Western Europe, Eastern Europe, North America, South America, Middle East, Africa |

| Country Scope | The countries covered in the report are Australia, Brazil, China, France, Germany, India, ... |

| Key Companies Profiled | Samsung Electronics Co. Ltd., Taiwan Semiconductor Manufacturing Company Limited, Intel Corporation, Qualcomm Inc., Fujitsu Limited, Toshiba Corporation, Applied Materials Inc., ASE Technology Holding Co. Ltd., Texas Instruments Incorporated, Lam Research Corporation, STMicroelectronics N.V., Infineon Technologies AG, NXP Semiconductors N.V., Analog Devices Inc., Renesas Electronics Corporation, United Microelectronics Corporation, GlobalFoundries Inc., Amkor Technology Inc., Microchip Technology Inc., Synopsys Inc, Xilinx Inc., Siliconware Precision Industries Co Ltd, Onto Innovation Inc., Unisem Group, Nepes Corporation, Deca Technologies Inc, Yield Engineering Systems Inc, Powertech Technology Inc., Jiangsu Changdian Technology Co. Ltd., Yole Group |

| Customization Scope | Request for Customization |

| Pricing And Purchase Options | Explore Purchase Options |